# AOZ71026QI

Two Rails Hybrid Low I<sub>Q</sub> Intel IMVP Controller for CPU

# **General Description**

The AOZ71026QI is a high performance digital & analog hybrid multiphase buck controller designed in compliance with Intel IMVP8, 9, and 9.1/9.2 platform specifications. It provides two output rails (up to 4 + 2) and supports 3 separate SVID domains. Up to 4 phases for core voltage domain (IA) and 2 phases for graphics voltage domain (GT) as well as the  $P_{\rm SYS}$  domain's reporting functions, incorporated into a single SVID interface. AOS offers a novel AOS Advanced Transient Modulator (A²TM). It combines an advanced variable frequency hysteretic peak current mode control with proprietary phase current sensing scheme for fast transient response and low system cost. The control loop enhances light-load efficiency by seamlessly entering DCM mode of operation.

The AOZ71026QI is equipped with SMBus digital Interface enabling register programming for tuning and configuration to minimize the system components and eliminate the need for manual solder rework on the system board. Programmability can be done either by AOS GUI or customized ECS into the controller's built-in RAM. The controller also provides MTP to store register settings once the configuration is finalized.

Combined with AOS high performance DrMOS, the AOZ71026QI provides a complete power solution for Intel IMVP9.1/9.2 mobile platform VCORE applications. AOZ71026QI comes in a 6 mm x 6 mm 48-pin QFN package.

The AOZ71026QI controller features very low power consumption while still enabling digital interface control. This unique "Hybrid Digital" control scheme enables low quiescent power consumption in all power states as defined by the Intel IMVP9.1 platform to enable long system run times in battery life workloads.

The AOZ71026QI provides complete protection and warning functions including UVP, OVP, OCP and OTP. Fault protection behavior can be easily programmed through SMBus. AOZ71026QI also offers real time telemetry information via SMBus for  $V_{\text{IN}},\,V_{\text{OUT}},$  temperature, output currents, power states as well as PSYS/VSYS/IAUX pins reporting via SMBus.

#### **Features**

- 5.2 V to 24 V V<sub>IN</sub> input supply voltage

- Dual output rails: 4/3/2/1 + 2/1 phases

- Digital & analog hybrid controller with SMBus programmability and lowest power consumption

- SVID Interface to CPU compliant with IMVP8, 9, and 9.1 /9.2 specifications

- Differential remote sensing to achieve 0.5% regulated

V<sub>OUT</sub> accuracy

- Low quiescent current: 1.95 mA at PS0 for 2+1 configuration

- 42 µA quiescent current at Intel PS4 state

- FCCM2 pin to lower power loss in unused phases in PS3 mode

- Supports multi-sourced industry standard DrMOS or driver + MOSFET power stages

- User friendly GUI for compensation and configurations with minimal external RC components.

- ECS programmability for configurations with Built-in MTP and RAM

- Proprietary, high performance AOS Advanced Transient Modulator (A<sup>2</sup>TM) control scheme:

- Variable frequency hysteretic peak current mode control gives fast transient response

- Dynamic phase current balance

- Excellent load-line control and phase current sensing

- Seamless CCM to DCM control to maximize efficiency

- System Input Power Monitoring (both P<sub>SYS</sub> and V<sub>SYS</sub>)

- 400 kHz to 1.1 MHz programmable switching frequency

- Acoustic Noise Suppression

- Output Under-Voltage Protection (UVP)

- Output Over-Voltage Protection (OVP)

- Over-Current Protection (OCP)

- Over-Temperature Protection (OTP)

- QFN6x6-48L package

### **Applications**

- Notebook computers

- Memory and graphic cards

- Video game console

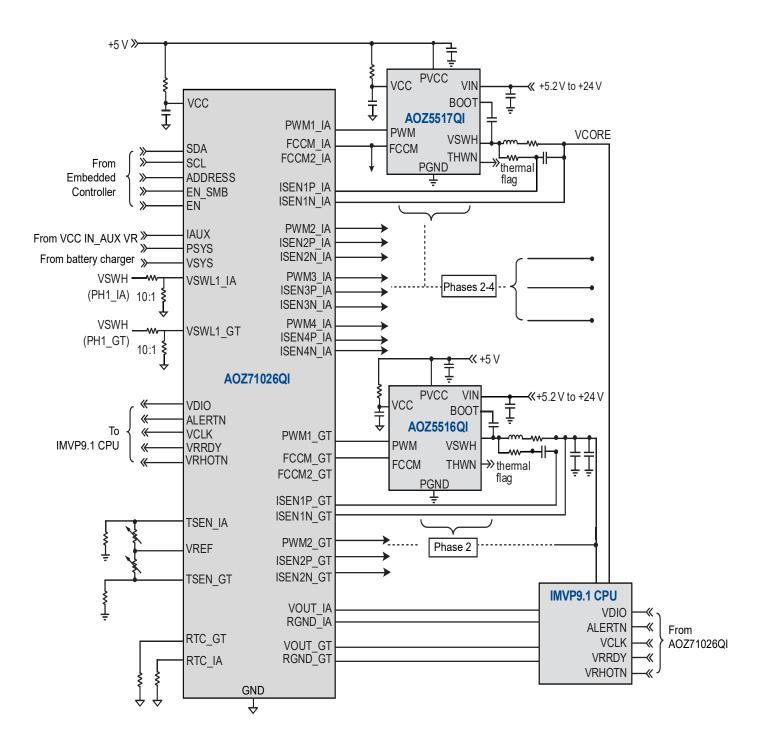

# **Typical Application**

### **Ordering Information**

| Part Number <sup>(1)</sup>    | Junction Temperature Range | Package    | Environmental |  |

|-------------------------------|----------------------------|------------|---------------|--|

| AOZ71026QI-xxx <sup>(2)</sup> | -40°C to +125°C            | QFN6x6-48L | RoHS          |  |

#### Notes:

- 1. For each customer, the full PN already created for order is on the last page of this DS. Please refer to last page for more information.

- 2. "xxx" is the configuration code identifier (also called sub-part number) for the register settings stored in the internal non-volatile memory (NVM). Each "x" can be a value between 0 and 9 and A-Z (except I, J, O, Q). Please work with an AOS Sales/FAE to create this unique number. Each project or board might need to use different sub-PN as the register setting might be different.

### Contact local sales office for full product datasheet.

AOS products are offered in packages with Pb-free plating and compliant to RoHS standards.

Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

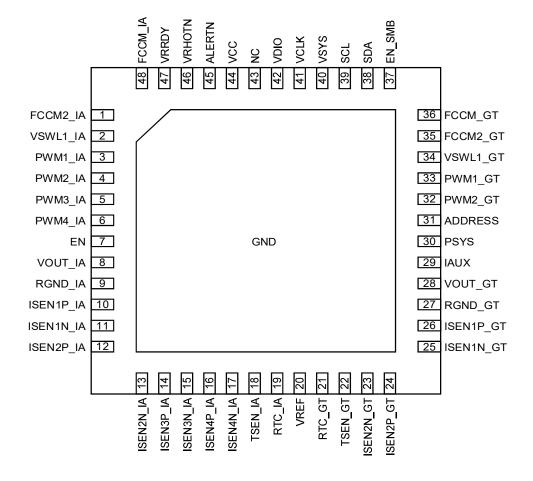

# **Pin Configuration**

Figure 1. QFN 6x6-48L (Top View)

Rev. 1.0 December 2021 www.aosmd.com Page 3 of 8

# **Pin Description**

| Pin Num | Pin Name  | I/O | Pin Function                                                                                                                                                                                                                                        |

|---------|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | FCCM2_IA  | 0   | Forced Continuous Current Mode for core domain. Connect to FCCM input of individual DrMOS on phases 2-N supplying power for core domain dedicated to low light operation. Continuous mode is active if FCCM is high. DrMOS is disabled if floating. |

| 2       | VSWL1_IA  | I   | Power conversion input voltage sensing for core domain. Connect to the switching node of phase 1 DrMOS through a 10:1 resistor divider.                                                                                                             |

| 3       | PWM1_IA   | 0   | Core voltage domain PWM signal for Phase 1. Connect to the PWM input of DrMOS.                                                                                                                                                                      |

| 4       | PWM2_IA   | 0   | Core voltage domain PWM signal for Phase 2. Connect to the PWM input of DrMOS.                                                                                                                                                                      |

| 5       | PWM3_IA   | 0   | Core voltage domain PWM signal for Phase 3. Connect to the PWM input of DrMOS.                                                                                                                                                                      |

| 6       | PWM4_IA   | 0   | Core voltage domain PWM signal for Phase 4. Connect to the PWM input of DrMOS.                                                                                                                                                                      |

| 7       | EN        | I   | Logic input to enable the controller. Active logic high.                                                                                                                                                                                            |

| 8       | VOUT_IA   | I   | Remote CPU core voltage sensing for control loop feedback and regulation. Connect to CPU prescribed pin.                                                                                                                                            |

| 9       | RGND_IA   | I   | Remote CPU core ground sensing for control loop feedback and regulation. Connect to CPU prescribed pin.                                                                                                                                             |

| 10      | ISEN1P_IA | I   | Positive node of core domain current feedback for droop regulation and output current monitoring for Phase 1. Connect to the center RC network across the inductor for DCR sensing.                                                                 |

| 11      | ISEN1N_IA | I   | Negative node of core domain current feedback for droop regulation and output current monitoring for Phase 1. Connect to the V <sub>OUT</sub> terminal of the inductor for DCR sensing.                                                             |

| 12      | ISEN2P_IA | I   | Positive node of core domain current feedback for droop regulation and output current monitoring for Phase 2. Connect to the center RC network across the inductor for DCR sensing.                                                                 |

| 13      | ISEN2N_IA | I   | Negative node of core domain current feedback for droop regulation and output current monitoring for Phase 2. Connect to the V <sub>OUT</sub> terminal of the inductor for DCR sensing.                                                             |

| 14      | ISEN3P_IA | I   | Positive node of core domain current feedback for droop regulation and output current monitoring for Phase 3. Connect to the center RC network across the inductor for DCR sensing.                                                                 |

| 15      | ISEN3N_IA | I   | Negative node of core domain current feedback for droop regulation and output current monitoring for Phase 3. Connect to the V <sub>OUT</sub> terminal of the inductor for DCR sensing.                                                             |

| 16      | ISEN4P_IA | I   | Positive node of core domain current feedback for droop regulation and output current monitoring for Phase 4. Connect to the center RC network across the inductor for DCR sensing.                                                                 |

| 17      | ISEN4N_IA | I   | Negative node of core domain current feedback for droop regulation and output current monitoring for Phase 4. Connect to the V <sub>OUT</sub> terminal of the inductor for DRC sensing circuit.                                                     |

| 18      | TSEN_IA   | I   | Core domain temperature sensing input. Connect a precision 1% resistor to GND and an NTC thermistor to VREF.                                                                                                                                        |

| 19      | RTC_IA    | I   | Core domain temperature gain sensing input. Connect a precision 1% resistor to GND and an NTC thermistor to VREF pin.                                                                                                                               |

| 20      | VREF      | 0   | 2.56 V reference voltage output. Connect NTC thermistors from TSEN_IA and TSEN_GT to this pin.                                                                                                                                                      |

| 21      | RTC_GT    | I   | Graphics domain temperature gain sensing input. Connect a precision 1% resistor to GND and an NTC thermistor to VREF pin.                                                                                                                           |

| 22      | TSEN_GT   | I   | Graphics domain temperature sensing input. Connect a precision 1% resistor to GND and an NTC thermistor to VREF.                                                                                                                                    |

| 23      | ISEN2N_GT | I   | Negative node of graphics domain current feedback for droop regulation and output current monitoring for Phase 2. Connect to the $V_{OUT}$ terminal of the inductor for DCR sensing.                                                                |

| 24      | ISEN2P_GT | I   | Positive node of graphics domain current feedback for droop regulation and output current monitoring for Phase 2. Connect to the center RC network across the inductor for DCR sensing.                                                             |

| 25      | ISEN1N_GT | I   | Negative node of graphics domain current feedback for droop regulation and output current monitoring for Phase 1. Connect to the V <sub>OUT</sub> terminal of the inductor for DCR sensing.                                                         |

# **Pin Description**

| Pin Num                                                                                      | Pin Name                                                                                                                                                                                                                                                                                                                                                                      | I/O                                                                                                                                                                                                  | Pin Function                                                                                                                                                                                                                                             |  |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 26                                                                                           | ISEN1P_GT                                                                                                                                                                                                                                                                                                                                                                     | I                                                                                                                                                                                                    | Positive node of graphics domain current feedback for droop regulation and output current monitoring for Phase 1. Connect to the center RC network across the inductor for DCR sensing.                                                                  |  |  |  |

| 27                                                                                           | RGND_GT                                                                                                                                                                                                                                                                                                                                                                       | I                                                                                                                                                                                                    | Remote CPU graphics ground sensing for control loop feedback and regulation. Connect to CPU prescribed pin.                                                                                                                                              |  |  |  |

| 28                                                                                           | VOUT_GT                                                                                                                                                                                                                                                                                                                                                                       | I                                                                                                                                                                                                    | Remote CPU graphics voltage sensing for control loop feedback and regulation. Connect to CPU prescribed pin.                                                                                                                                             |  |  |  |

| 29                                                                                           | IAUX                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                    | Current monitor input from VCCIN_AUX rail. Input analog signal will be converted to digital signal and communicated to the CPU through SVID Bus via the PSYS domain.                                                                                     |  |  |  |

| 30                                                                                           | PSYS                                                                                                                                                                                                                                                                                                                                                                          | I                                                                                                                                                                                                    | System power monitor input from Battery Charger. Input analog signal will be converted to digital signal and communicate with CPU through SVID Bus via the PSYS domain.                                                                                  |  |  |  |

| 31                                                                                           | ADDRESS                                                                                                                                                                                                                                                                                                                                                                       | Ι                                                                                                                                                                                                    | SMBus address select pin. Tie high for address 0x62, low for 0x26. Should neither of these be usable, the pin can also be left floating to give a factory configured default.                                                                            |  |  |  |

| 32 PWM2_GT O Graphics voltage domain PWM signal for Phase 2. Connect to the PWM input of DrN |                                                                                                                                                                                                                                                                                                                                                                               | Graphics voltage domain PWM signal for Phase 2. Connect to the PWM input of DrMOS.                                                                                                                   |                                                                                                                                                                                                                                                          |  |  |  |

| 33                                                                                           | PWM1_GT                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                    | Graphics voltage domain PWM signal for Phase 1. Connect to the PWM input of DrMOS.                                                                                                                                                                       |  |  |  |

| 34                                                                                           | phase 1 DrMOS through a 10:1 resistor divider.  Forced Continuous Current Mode for graphics domain. Connect to FCCM input of inc DrMOS on phase 2 supplying power for graphics domain dedicated to low light opera Continuous mode is active if FCCM is high. DrMOS is disabled if floating.  Forced Continuous Current Mode for graphics domain. Connect to FCCM input of Ph |                                                                                                                                                                                                      | Power conversion input voltage sensing for graphics domain. Connect to the switching node of phase 1 DrMOS through a 10:1 resistor divider.                                                                                                              |  |  |  |

| 35                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                      | Forced Continuous Current Mode for graphics domain. Connect to FCCM input of individual DrMOS on phase 2 supplying power for graphics domain dedicated to low light operation. Continuous mode is active if FCCM is high. DrMOS is disabled if floating. |  |  |  |

| 36                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                      | Forced Continuous Current Mode for graphics domain. Connect to FCCM input of Phase 1's DrMOS supplying power for graphics domain. Continuous mode is active if FCCM is high. Discontinuous mode is active is low. DrMOS is disabled if floating.         |  |  |  |

| 37                                                                                           | EN_SMB I SMBus enable input. Connect to VCC to allow SMBus register read/write.                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                      | SMBus enable input. Connect to VCC to allow SMBus register read/write.                                                                                                                                                                                   |  |  |  |

| 38                                                                                           | SDA                                                                                                                                                                                                                                                                                                                                                                           | SDA I/O SMBus data line. Open drain I/O. Connect a precision 1% resistor to VCC.                                                                                                                     |                                                                                                                                                                                                                                                          |  |  |  |

| 39                                                                                           | SCL                                                                                                                                                                                                                                                                                                                                                                           | CL I/O SMBus clock line, Open drain input. Connect a precision 1% resistor to VCC.                                                                                                                   |                                                                                                                                                                                                                                                          |  |  |  |

| 40                                                                                           | VSYS                                                                                                                                                                                                                                                                                                                                                                          | VSYS  I System power monitor input voltage level from battery output. Input analog signal will be converted to digital signal and communicate with CPU through SVID Bus via the P <sub>SYS</sub> dom |                                                                                                                                                                                                                                                          |  |  |  |

| 41                                                                                           | VCLK                                                                                                                                                                                                                                                                                                                                                                          | I/O                                                                                                                                                                                                  | SVID clock line. Open drain input. Communication line to CPU.                                                                                                                                                                                            |  |  |  |

| 42                                                                                           | VDIO                                                                                                                                                                                                                                                                                                                                                                          | I/O                                                                                                                                                                                                  | SVID data line. Open drain I/O. Communication line to CPU.                                                                                                                                                                                               |  |  |  |

| 43                                                                                           | NC                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                      | No Connect.                                                                                                                                                                                                                                              |  |  |  |

| 44                                                                                           | VCC                                                                                                                                                                                                                                                                                                                                                                           | - 1                                                                                                                                                                                                  | Power supply for the controller. Connect a 1µF MLCC capacitor to GND.                                                                                                                                                                                    |  |  |  |

| 45                                                                                           | ALERTN                                                                                                                                                                                                                                                                                                                                                                        | I/O                                                                                                                                                                                                  | VR Alert: Active low open drain output to CPU. Notification signal to indicate all SVID alert conditions.                                                                                                                                                |  |  |  |

| 46                                                                                           | VRHOTN O VR HOT: Active low open drain output to CPU. Notification signal to indicate the syste temperature is too high.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                      | VR HOT: Active low open drain output to CPU. Notification signal to indicate the system temperature is too high.                                                                                                                                         |  |  |  |

| 47                                                                                           | VRRDY                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                    | VR Ready: Open drain output to CPU. Notification signal to indicate both core and graphics output voltage are ready.                                                                                                                                     |  |  |  |

| 48                                                                                           | FCCM_IA                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                    | Forced Continuous Current Mode for core domain. Connect to FCCM input of phase 1's DrMOS supplying power for core domain. Continuous mode is active if FCCM is high. Discontinuous mode is active is low. DrMOS is disabled if floating.                 |  |  |  |

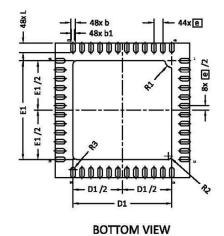

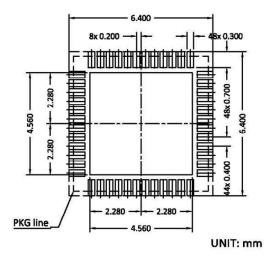

# Package Dimensions, QFN6X6-48L

SIDE VIEW

### RECOMMENDED LAND PATTERN

| CVAADOLC | DIM. IN MILLIMETERS |       |          | DIM. IN INCHES  |       |       |

|----------|---------------------|-------|----------|-----------------|-------|-------|

| SYMBOLS  | MIN                 | NOM   | MAX      | MIN             | NOM   | MAX   |

| Α        | 0.850               | 0.900 | 0.950    | 0.033           | 0.035 | 0.037 |

| A1       | 0.000               |       | 0.050    | 0.000           |       | 0.002 |

| b        | 0.150               | 0.200 | 0.250    | 0.006           | 0.008 | 0.010 |

| b1       |                     |       | 0.007REF | EF              |       |       |

| С        |                     |       | 0.008REF |                 |       |       |

| D        | 5.900               | 6.000 | 6.100    | 0.232           | 0.236 | 0.240 |

| D1       | 4.350               | 4.400 | 4.450    | 0.171           | 0.173 | 0.175 |

| E        | 5.900               | 6.000 | 6.100    | 0.232           | 0.236 | 0.240 |

| E1       | 4.350               | 4.400 | 4.450    | 0.171           | 0.173 | 0.175 |

| Ĺ        | 0.400               | 0.450 | 0.500    | 500 0.016 0.018 | 0.018 | 0.020 |

| R1       | 0.250               | 0.300 | 0.350    | 0.010           | 0.012 | 0.014 |

| R2       | 0.100               | 0.150 | 0.200    | 0.004           | 0.006 | 0.008 |

| R3       | 0.050               | 0.100 | 0.150    | 0.002           | 0.004 | 0.006 |

| e        | 0.400BSC            |       | 0.016BSC |                 |       |       |

NOTES: CONTROLLING DIMENSION IS MILLIMETER. CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

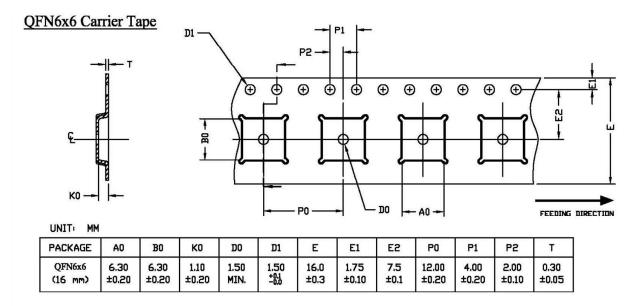

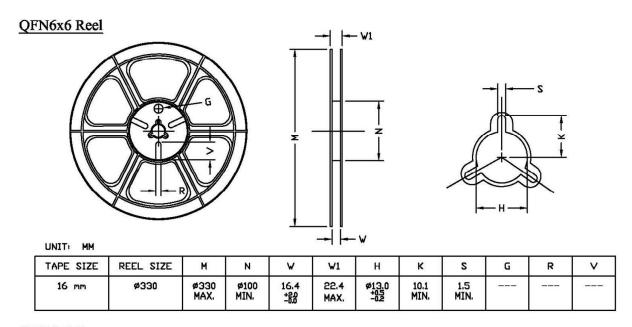

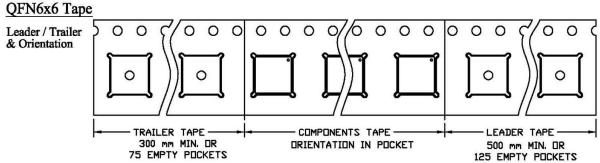

# Tape and Reel Dimensions, QFN6X6-48L

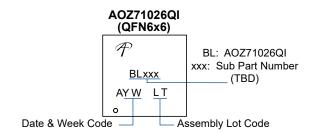

### Part Marking

| Sub PN<br>Marking | SKU                | Project Descriptions | Full PN        |  |

|-------------------|--------------------|----------------------|----------------|--|

| XXX               | ADL 28W Perf (3+2) |                      | AOZ71026QI-xxx |  |

### LEGAL DISCLAIMER

Applications or uses as critical components in life support devices or systems are not authorized. Alpha and Omega Semiconductor does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS's products are provided subject to AOS's terms and conditions of sale which are set forth at: http://www.aosmd.com/terms\_and\_conditions\_of\_sale

### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or device, or system whose failure to perform can be (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

2. A critical component in any component of a life support, reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev. 1.0 December 2021 Page 8 of 8 www.aosmd.com